## Presented by TestEquity - www.TestEquity.com

# The Basics of Serial Data Compliance and Validation Measurements

Primer

Primer

#### **Table of Contents**

| Design Standard.4ConnectivityA Range of Serial Standards.4 - 9TriMode™ Differential ProbesSATA/SAS.4Pseudo-differentially Connected Moveable ProbesPCI Express®.6SMA Pseudo-differentially Connected ProbesEthernet.6SMA Pseudo-differentially Connected ProbesUSB.7True Differential Moveable ProbesUSB.7SMA True Differential ProbesHDMI/DisplayPort.7SMA True Differential ProbesCommon Architectural Elements.8Pattern GenerationDifferential Transmission.8Pattern Generation8b/10b Signal Encoding.8The Test ProcessEmbedded Clocks.8Seeing Inside the ReceiverDe-Emphasis.9Receiver Amplitude Sensitivity MeasurementsLow Voltage Signaling.9Receiver Timing MeasurementsNext-generational Serial Challenges.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14<br>14<br>15<br>15<br>16<br>16<br>17<br>17<br>18 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| A Range of Serial Standards  SATA/SAS  PCI Express®  Ethernet  USB  HDMI/DisplayPort  Common Architectural Elements  Differential Transmission  8b/10b Signal Encoding  Embedded Clocks  De-Emphasis  Low Voltage Signaling  Pseudo-differentially Connected  Moveable Probes  SMA Pseudo-differentially Connected Probes  SMA Pseudo-differentially Connected Probes  True Differential Moveable Probes  SMA True Differential Probes  Fixtures  Pattern Generation  Receiver Sensitivity Testing  The Test Process  Seeing Inside the Receiver  Receiver Amplitude Sensitivity Measurements  Receiver Timing Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14<br>15<br>15<br>16<br>16<br>17<br>17<br>18       |

| SATA/SAS PSeudo-differentially Connected Moveable Probes  PCI Express® 6 Ethernet 6 USB 7 HDMI/DisplayPort 7 Common Architectural Elements Differential Transmission 8b/10b Signal Encoding Embedded Clocks De-Emphasis Low Voltage Signaling  Pseudo-differentially Connected Moveable Probes  SMA Pseudo-differentially Connected Probes  SMA Pseudo-differentially Connected Probes  SMA Pseudo-differentially Connected Moveable Probes  SMA True Differential Probes  Fixtures  Pattern Generation Receiver Sensitivity Testing The Test Process Seeing Inside the Receiver Receiver Amplitude Sensitivity Measurements  Receiver Timing Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15<br>15<br>16<br>16<br>17<br>17<br>18             |

| PCI Express® .6 SMA Pseudo-differentially Connected Probes Ethernet .6 USB .7 True Differential Moveable Probes SMA True Differential Moveable Probes SMA True Differential Moveable Probes | 15<br>15<br>16<br>16<br>17<br>17<br>18             |

| Ethernet6 USB7 HDMI/DisplayPort7 Common Architectural Elements8 Differential Transmission8 8b/10b Signal Encoding8 Embedded Clocks8 De-Emphasis9 Low Voltage Signaling9  SMA Fseudo-differentially Collificated Flobes True Differential Moveable Probes SMA True Differential Probes SMA True Differential Probes Fixtures Pattern Generation Receiver Sensitivity Testing The Test Process Seeing Inside the Receiver Receiver Amplitude Sensitivity Measurements Receiver Timing Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>15<br>16<br>16<br>17<br>17<br>18             |

| USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15<br>16<br>16<br>17<br>17<br>18                   |

| HDMI/DisplayPort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16<br>17<br>17<br>18<br>18                         |

| Common Architectural Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16<br>17<br>17<br>18<br>18                         |

| Differential Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17<br>17<br>18<br>18                               |

| 8b/10b Signal Encoding .8 The Test Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17<br>18<br>18                                     |

| Embedded Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18<br>18                                           |

| De-Emphasis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18                                                 |

| Low Voltage Signaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

| Descriped little Telegraph Managements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                                                 |

| Next-generational Serial Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19                                                 |

| Gigabit Speeds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                 |

| Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

| Transmission Line Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                 |

| Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                 |

| Compliance Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21                                                 |

| Eye Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                 |

| Amplitude Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                                                 |

| Timing Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                 |

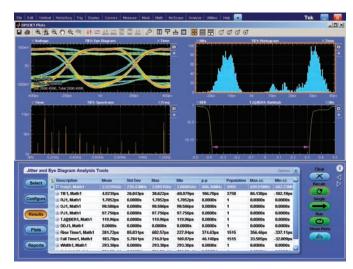

| Jitter Tests 12 Jitter Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                                                 |

| Receiver Sensitivity Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                 |

| Circuit Board and Interconnect Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                 |

| SSC Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                 |

| Transmission Media Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                                                 |

| De-embedding/Normalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26                                                 |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27                                                 |

Further Reading ......27

# Serial Buses - An Established Design Standard

High-speed serial bus architectures are the new norm in today's high-performance designs. While parallel bus standards are undergoing some changes, serial buses are established across multiple markets – computers, cell phones, entertainment systems, and others – and offer performance advantages, lower cost, and fewer traces in circuit and board designs and layouts.

You might already have experience with first- and second-generation serial bus standards, like 2.5 Gb/s PCI Express® (PCIe) and 3 Gb/s Serial ATA (SATA). Engineers are now looking at the requirements in designing to third-generation specifications, including PCI Express 3.0 (8 Gb/s), that are still evolving in working groups.

Serial buses continue to advance with faster edge rates and a narrower unit interval (UI), creating unique, exacting demands on your design, compliance testing, and debug processes. Standards have reached speeds at which you need to be ready for RF analog characteristics and transmission line effects that have a far bigger impact on the design than in the past.

Faster transition times, shorter UIs, different pathway impedances, and noise sources in the amplitude domain all contribute more to bit error rate and add up to engineers needing to take a fresh look at their strategies for connectivity, pattern generation, receiver-side testing, data acquisition, and analysis. Coupling these issues with evolving standards and tighter compliance testing requirements creates a tougher job for companies to quickly get their products to market.

In this primer, we look at the compliance requirements of serial standards, with focus on the issues of next generation standards. After introducing the characteristics of several key standards, we'll look at the issues you face, including basic tests, and what you need to consider during the compliance testing and debug phases. We'll address five main areas: connecting to the device under test (DUT), generating accurate test patterns, testing receivers, acquiring data, and analyzing it.

## A Range of Serial Standards

Across the electronics industry, manufacturers and other companies have introduced serial bus standards for multiple purposes to address the needs of their markets and customers. A key objective of the standards is to enable interoperability within an architecture across a wide range of products offered by a host of vendors. Each standard is managed by a governing body with committees and working groups to establish design and testing requirements. Table 1 lists some of the key serial standards.

Each specification defines attributes that products must comply with to meet the standard's requirements, including electrical, optical (if applicable), mechanical, interconnects, cable and other pathway losses, and many others. The governing body issues standardized tests that products must pass for compliance to the standard. The tests might be detailed to the point of requiring specific test equipment, or they might be more general and allow the designer/manufacturer to determine appropriate characteristics to be compliant. Specifications undergo change as the standards evolve. You must keep current your knowledge of the specification's requirements.

Tektronix is involved with many standards organizations and participates along with other companies in different working groups to help governing bodies establish effective testing processes and procedures for compliance testing.

In this document, we'll refer to the following three standards. Tektronix is involved in working groups in each of these standards.

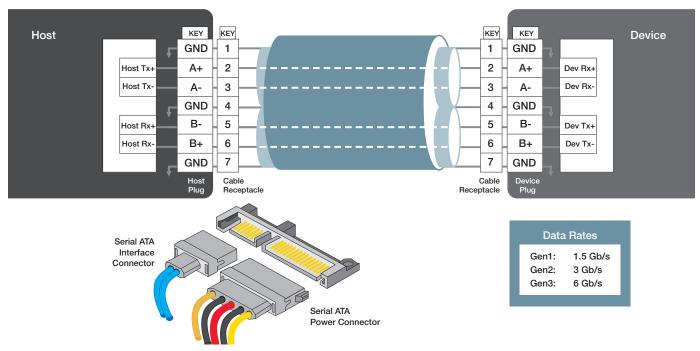

#### SATA/SAS

SATA is a serial standard for attached storage, widely used in today's desktop PCs and other computing platforms. It was initially released at 1.5 Gb/s, then was increased to 3 Gb/s with second generation (Gen2). Third generation SATA (6 Gb/s) devices recently entered the market. Serial Attached SCSI (SAS), like SATA, is a serial standard for storage applications. SAS designs, however, are primarily used in data center and enterprise applications. SAS operates at 3 Gb/s and SAS2 doubles that rate to 6 Gb/s.

| Purpose                                    | Standard                                                              | Governing Body                                                                                                                          |                                                                       |

|--------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Attached storage access                    | Serial ATA (SATA)<br>Serial-attached SCSI (SAS)                       | SATA-IO<br>SCSI Trade Association                                                                                                       | www.sata-io.org<br>www.scsita.org                                     |

| Chip-to-chip<br>and module<br>interconnect | PCI Express® (PCIe)<br>RapidIO                                        | PCI-SIG<br>Rapid I/O Trade Association                                                                                                  | www.pcisig.org<br>www.rapidio.org                                     |

| High-definition<br>display                 | High-Definition Multimedia<br>Interface (HDMI)<br>DisplayPort         | HDMI Video Electronics Standards Association (VESA)                                                                                     | www.hdmi.org<br>www.vesa.org                                          |

| Systems<br>interconnect                    | InfiniBand<br>Fibre Channel<br>Ethernet<br>Universal Serial Bus (USB) | InfiniBand Trade Association<br>International Committee for Information Technology Standards<br>IEEE<br>USB Implementers Forum (USB-IF) | www.infinibandta.org<br>www.incits.org<br>www.ieee.org<br>www.usb.org |

Table 1. Key Serial Standards.

Figure 1. SATA mechanical layout.

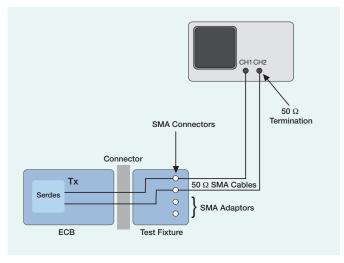

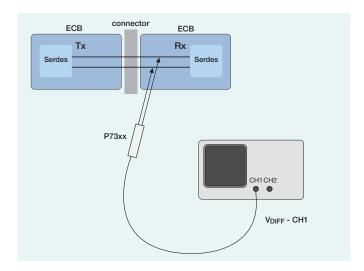

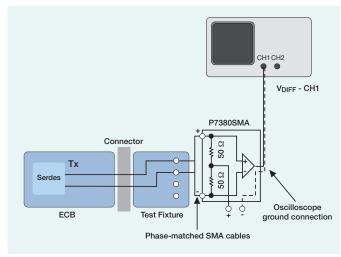

Figure 1 illustrates the SATA signals and mechanical layout. Like many serial standards, SATA and SAS uses low-voltage differential signaling (LVDS) and 8b/10b encoding. Data travels between transmitters and receivers over

dual-simplex channels; the link consists of one lane of transmit and receive pair. SATA uses a spread-spectrum clock (SSC) in an embedded clocking scheme without a separate reference clock transmitted to the receiver.

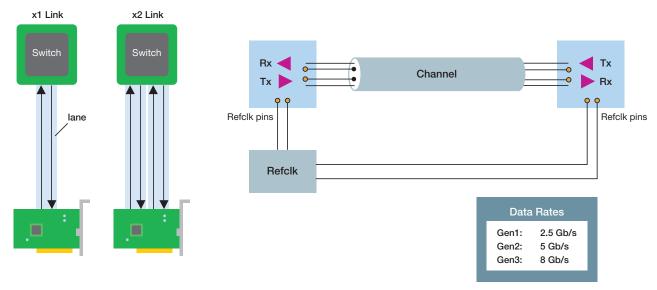

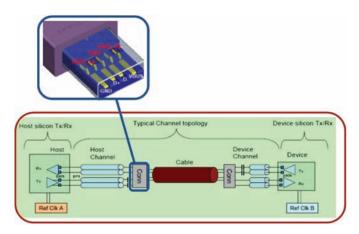

Figure 2. PCI Express® architecture

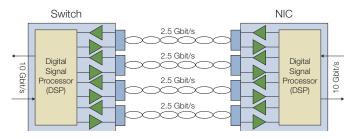

Figure 3. 10GBASE-T Ethernet architecture.

## PCI Express®

PCI Express has replaced PCI in most chip-to-chip applications, including pathways crossing circuit boards and cable connections. PCIe is a highly scalable architecture, providing from one to 16 dual-simplex lanes in a PCIe link. In multi-lane applications, the data stream is divided up amongst the available lanes and transmitted nearly simultaneously at the lane rate. The fastest PCIe applications are typically used in graphics, connecting 16 lanes of high-speed, high-resolution graphical data between a system's chipset and a graphics processor. Figure 2 illustrates the PCI Express architecture.

The first-generation per-lane transfer rate for PCle is 2.5 Gb/s with PCle 2.0 providing 5 Gb/s rates. Soon there will be products with 8 Gb/s transfer rates for PCle third generation. PCle embeds the clock in the data stream, but also couples a reference clock to drive the PLL reference input on the receiver.

#### **Ethernet**

Ethernet is a Local Area Network (LAN) technology defined by the IEEE 802.3 standard and is a widely adopted standard for communication between multiple computers. Ethernet interfaces varies from application to application and includes both electrical (twisted-pair cable, copper backplane) and optical (multimode fiber) signaling media. Currently the most popular Ethernet interface is Unshielded Twisted Pair (UTP).

First- and second-generation Ethernet standards, 10BASE-T and 100BASE-T, provide a transfer rate of 10 Mb/s and 100 Mb/s respectively. Broad deployment of Gigabit Ethernet (1000 Mb/s) is under way with 10GBASE-T designs emerging soon. The 10GBASE-T specification employs full duplex baseband transmission over four pairs of balanced cabling. The aggregate data rate of 10 Gb/s is achieved by transmitting 2500 Mb/s in each direction simultaneously on each wire pair as shown in Figure 3.

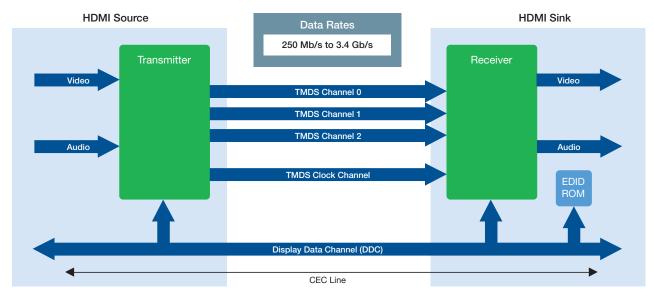

Figure 4. HDMI architecture.

Figure 5. USB Architecture.

#### **USB**

Universal Serial Bus has become known as the de facto standard for connecting personal computers and other peripheral devices. USB 2.0 (480 Mb/s) was adopted in 2000 with 40x speed improvement over the legacy USB 1.1 (12 Mb/s) specification. Recently the USB 3.0 or SuperSpeed USB specification was introduced at a 10x improvement over USB 2.0. With a 5 Gb/s data rate SuperSpeed USB will accommodate data-intensive applications like High Definition video and fast I/O to flash memory devices. Because of the large adoption of legacy USB products USB 3.0 provides complete backwards compatibility. Figure 5 shows the link architecture for SuperSpeed USB.

#### HDMI/DisplayPort

The High Definition Multimedia Interface (HDMI) is the first specification designed specifically to address the needs of the consumer entertainment systems market. HDMI builds on the highly successful Digital Video Interface (DVI) for PCs and extends it with additional capabilities for home entertainment devices, like large-screen, high-definition TVs and home theater systems. Figure 4 illustrates the HDMI architecture.

HDMI transmits high-resolution video and multi-channel audio from a source to a sink. The specification defines three data channels in the HDMI link with transmission rates from 250 Mb/s to 3.4 Gb/s, depending on the display resolution.

While most high-speed serial standards rely on LVDS with 8b/10b encoding, HDMI uses transition-minimized differential signaling, or TMDS, to reduce the number of transitions on a link and minimize electromagnetic interference (EMI).

HDMI also uses a reference clock transmitting at 1/10th the data rate. A low-speed serial bus (I<sup>2</sup>C), called the DDC bus, exchanges configuration and identification data bi-directionally between the source and sink.

The DisplayPort specification defines a scalable digital display interface with optional audio- and content-protection capability for broad usage within business, enterprise, and consumer applications. The interface is includes support for two data rates: Reduced Bit Rate (1.62 Gb/s) and High Bit Rate (2.7 Gb/s).

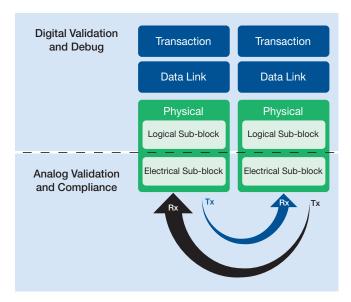

Figure 6. Layered model.

#### Common Architectural Elements

All the high-speed serial standards follow a layered model, as illustrated in Figure 6. The Physical layer comprises an electrical and logical sub-block. This primer focuses on the electrical sub-block, where electrical compliance testing is completed.

Many high-speed serial standards incorporate the same or similar architecture elements at the electrical level, such as:

- Differential signaling (LVDS or TMDS) for high data rates and high noise immunity

- 8b/10b encoding to improve signal integrity and reduce EMI

- Embedded clocks and some with reference clocks

- Spread-spectrum clocking to reduce EMI

- Equalization to compensate for signal attenuation from lossy channels

- Typical measurements include jitter, amplitude, differential skew, risetime/falltime, and common mode

- Specifications and testing requirements evolve as more insight is gained and the standards advance

Table 2 lists some of the architectures' key elements and compliance tests.

#### **Differential Transmission**

Differential transmission has been a part of communications technology since the early days of telephone networks. A differentially-transmitted signal consists of two equal and opposite versions of the waveform traveling down two conductors to a differential receiver1. When the signal on one leg of the differential path is going positive, the signal on the other leg is going equally negative, as shown in Figure 2. These two mirror images of the signal combine at the destination. Differential techniques resist crosstalk, externally induced noise, and other degradations. Properly designed and terminated, a differential architecture provides a robust path for sensitive high-frequency signals.

#### 8b/10b Signal Encoding

Many serial standards employ 8B/10B encoding, an IBM patented technology used to convert 8-bit data bytes into 10-bit Transmission Characters. These Transmission Characters improve the physical signal to bring about several key benefits: bit synchronization is more easily achieved; the design of receivers and transmitters is simplified; error detection is improved; and control characters (such as the Special Character) can be more readily distinguished from data characters.

#### **Embedded Clocks**

Many (if not most) current serial devices rely on embedded clock signals to maintain synchronization between transmitting and receiving elements. There is no separate clock signal line; instead, the timing information resides in the data signal. As we will see later in this document, this imposes certain requirements on the data signal. Encoding methods such as 8b/10b are used to guarantee that usable reference edges occur regularly enough to provide the needed synchronization.

|                          |                               | Inside t    | the Box    | Outside the Box |            |              | Display    |         |          |             |          |  |

|--------------------------|-------------------------------|-------------|------------|-----------------|------------|--------------|------------|---------|----------|-------------|----------|--|

|                          | Applications                  | PCI Express | Serial ATA | Ethernet        | Xaui       | FibreChannel | InfiniBand | USB 3.0 | 1394B    | DisplayPort | HDMI     |  |

|                          | Data Rate (maximum)           | 8 Gb/s      | 6 Gb/s     | 10 Gb/s         | 3.125 Gb/s | 2.125 Gb/s   | 2.5 Gb/s   | 5 Gb/s  | 800 Mb/s | 2.7 Gb/s    | 3.4 Gb/s |  |

|                          | Lanes                         | up to 16    | 1          | 1               | 4          | 1            | up to 12   | 1       | 1        | 4           | 3        |  |

|                          | Encoding                      | 8B10B       | 8B10B      |                 | 8B10B      | 8B10B        | 8B10B      | 8B10B   | 8B10B    | 8B10B       | 8B10B    |  |

|                          | Signaling                     | LVDS        | LVDS       |                 | LVDS       | LVDS         | LVDS       |         |          | LVDS        | TMDS     |  |

|                          | Embedded Clock                |             | •          |                 | •          | •            | •          | •       |          |             |          |  |

|                          | Sensitivity/Amplitude         |             | •          | •               | •          |              | •          | •       | •        |             | •        |  |

| Receiver/Sink Tests      | Timing Skew                   |             | •          |                 |            |              | •          |         | •        |             | •        |  |

| er/Sink                  | De-Emphasis                   |             |            | •               | •          |              | •          | •       |          |             |          |  |

| Receiv                   | PLL Loop Bandwidth            |             | •          | •               | •          |              | •          | •       |          |             |          |  |

|                          | Jitter Tolerance              |             | •          | •               | •          |              | •          | •       |          |             | •        |  |

|                          | Eye Diagram                   |             |            |                 | •          |              | •          | •       |          |             | •        |  |

| χ                        | Transition Timing (Rise/Fall) |             | •          |                 | •          |              | •          | •       | •        |             | •        |  |

| ce Test                  | Amplitude                     |             | •          | •               | •          | •            | •          | •       | •        |             | •        |  |

| r/Sour                   | Common Mode                   |             | •          | •               |            | •            | •          |         |          | •           |          |  |

| Transmitter/Source Tests | De-Emphasis                   |             |            |                 |            | •            | •          |         |          |             |          |  |

| Tran                     | Jitter                        |             | •          | •               | •          | •            | •          | •       |          |             | •        |  |

|                          | Return Loss                   |             | •          | •               |            |              |            |         |          |             |          |  |

| ests                     | Cross Talk                    |             | •          |                 |            | •            | •          | •       |          |             | •        |  |

| Cable/Connector Tests    | Transition Timing (Rise/Fall) |             | •          |                 |            | •            | •          |         |          |             | •        |  |

| /Conn                    | Loss                          |             | •          |                 | •          |              | •          | •       |          |             | •        |  |

| Cable                    | Impedance                     |             | •          |                 | •          | •            | •          | •       | •        |             | •        |  |

Table 2. Summary of common elements and tests of serial standards.

#### De-Emphasis

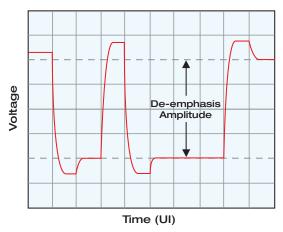

A technique known as de-emphasis modifies certain bits in a given sequence. That is, the first bit following a series of bits having the opposite state is higher in amplitude than subsequent bits. These subsequent bits, then, are de-emphasized. The purpose of this practice is to counteract frequency dependent losses in transmission media such as FR4 circuit boards.

#### Low Voltage Signaling

Modern serial architectures that employ differential transmission also use low-voltage signaling. Not surprisingly, the approach is known as Low Voltage Differential Signaling, or LVDS. Fast buses often rely on very low-voltage signals simply because it takes less time to change states over the span of a few hundred millivolts, for example, than it takes to make a full one-volt transition. Outwardly this might seem more susceptible to interference and noise, but differential transmission protects against such effects.

## Next-generation Serial Challenges

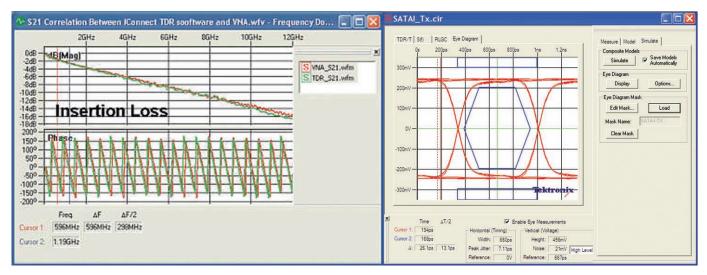

At the data rates next-generation serial standards operate, analog anomalies of the signal have a greater impact on signal integrity and quality than ever before. Conductors in signal pathways, including circuit board traces, vias, connectors, and cabling, exhibit greater transmission line effects with return losses and reflections that degrade signal levels, induce skewing, and add noise.

#### Gigabit Speeds

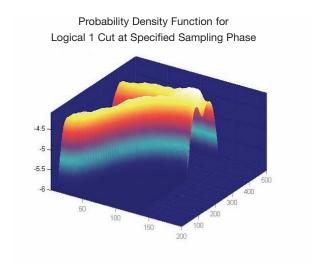

With each increase in transfer rates of the standards, the UI shrinks, and the tolerances in transmitter signal quality and receiver sensitivity become tighter. Low-voltage differential signals and multi-level signaling are more vulnerable to signal integrity issues, differential skew, noise, and inter-symbol interference (ISI) as speeds increase. There is greater susceptibility to timing problems, impedance discontinuities between a transmitter and receiver, and system level interaction between hardware and software. Multi-lane architectures amplify design complexity and potential for lane skew timing violations and crosstalk.

#### **Jitter**

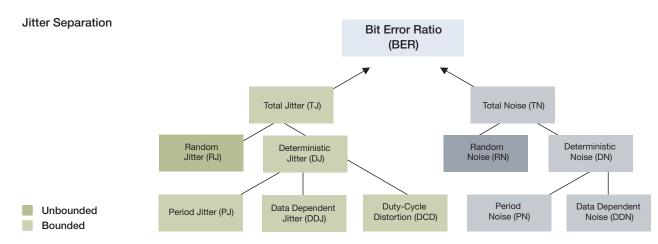

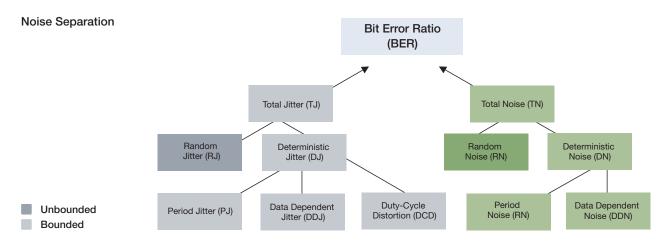

Today's higher data rates and embedded clocks mean greater susceptibility to jitter, degrading bit error rate (BER) performance. Jitter typically comes from crosstalk, system noise, simultaneous switching outputs, and other regularly occurring interference signals. With faster rates, multi-lane architectures, and more compact designs, there are more opportunities for all these events to affect data transmission in the form of signal jitter.

#### Transmission Line Effects

The signal transmitter, conductor pathways, and receiver constitute a serial data network. Buried in that network are distributed capacitance, inductance, and resistance that have diverse effects on signal propagation as frequencies increase. Transmission line effects rise from this distributed network and can significantly impact signal quality and lead to data errors.

#### Noise

Noise is unwanted aberrations in the amplitude domain that appear in the signal. Noise comes from both external sources, such as the AC power line, and internal sources, including digital clocks, microprocessors, and switched-mode power supplies. Noise can be transient or broadband random noise and can lead to phase errors and signal integrity problems. Like jitter in the frequency domain, with faster signaling, noise in the amplitude domain adds variations that can have a critical impact on BER performance.

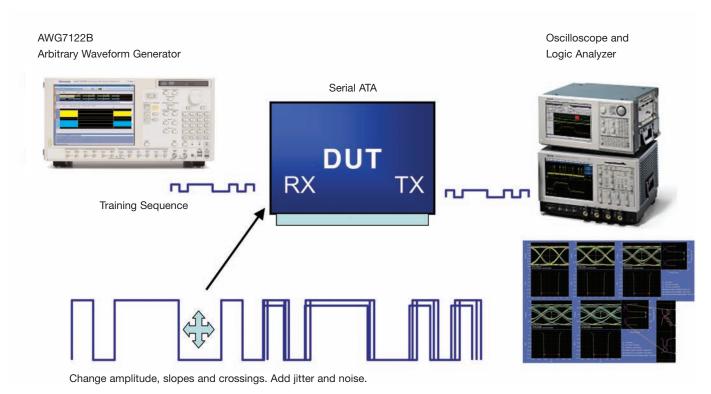

## Compliance Testing

Serial standards normally include amplitude, timing, jitter, and eye measurements within their compliance testing specifications. The latest versions of some standards add focus, compared to previous versions, on SSC clocking, receiver sensitivity testing, and measurement of return loss and reflections on connectors, cables, and other pathways. Not all measurements are required for compliance with every standard.

Test points are specified in the standard's compliance test document or the specification itself.

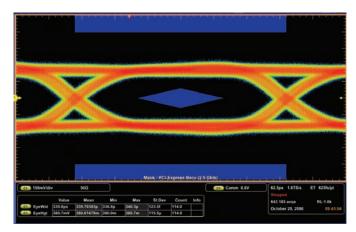

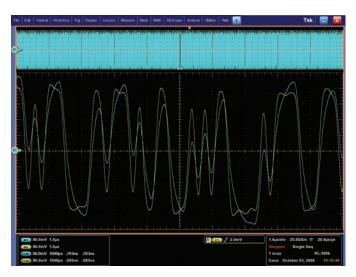

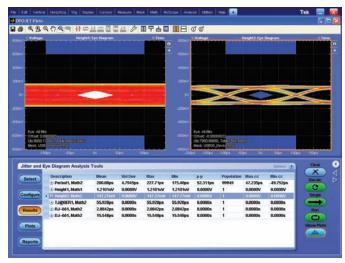

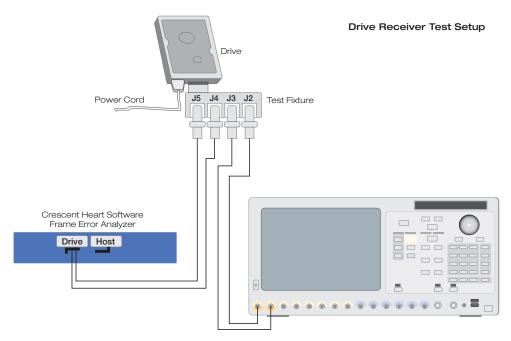

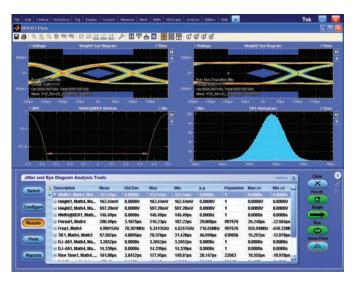

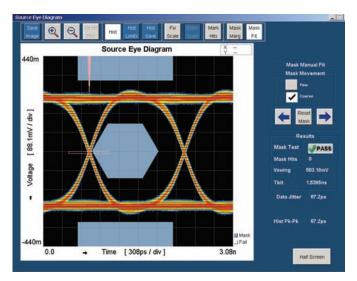

Figure 7. Eye diagram on an oscilloscope.

### Eye Measurements

Key compliance verification comes from eye measurements. An eye diagram is shown in Figure 7. Eye measurements result from superimposing multiple, one unit interval (UI) signal captures (the equivalent of one clock cycle) of the data stream, triggered to the recovered clock. Failure zones in the middle of the eye and above and below the eye are typically indicated by a "mask" (blue areas), showing the boundaries the test must not violate. Eye measurements are further discussed in the Analysis section later in this document.

The following tables encapsulate some of the key measurements commonly required at plug-fests (to prove compliance and interoperability) and ultimately, in certified compliance verification procedures.

#### **Amplitude Tests**

The amplitude tests listed in Table 3 verify that the signal achieves the voltage levels and stability to reliably propagate through the transmission media and communicate a proper "one" or "zero" to the receiver.

| Test                            | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential Voltage            | Every specification defines peak-to-peak differential voltage. This is the fundamental specification to guarantee that the transmitter is generating the correct voltage levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Eye Height                      | Eye height is the eye opening in the amplitude domain; it represents the amplitude at the sample point of the receiver circuit. Eye height is measured at the .5 Ul point, as referenced to the recovered clock. Eye diagrams are covered in more detail in the section on Analysis later in this document.                                                                                                                                                                                                                                                                                                                                               |

| De-Emphasis                     | During signal propagation, the transmission media can roll off and/or slow down the slew of a bit transitioning low to high or high to low. To compensate for this effect, the transmitter generates transition bits with slightly higher amplitude than follow-on bits of the same value. By making the transition bit higher in amplitude than the subsequent bits, the signal arrives at the receiver pins with an "open eye."  De-emphasis is the ratio of amplitudes between the second and subsequent bits following a transition bit and the transition bit (Figure 8). Other terms for de-emphasis are pre-emphasis and transmitter equalization. |

| Common Mode<br>Voltage (AC, DC) | Common mode imbalance and noise on the transmitter can create undesirable effects in the differential signal. It is often useful to break apart the differential signal into its single-ended components to troubleshoot such issues. This technique also pinpoints crosstalk and noise effects that may be coupling into one side of the differential pair and not the other.                                                                                                                                                                                                                                                                            |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 3. Overview of Amplitude Tests.

Figure 8. De-emphasis on a data stream.

#### **Timing Tests**

The timing tests listed in Table 4 verify the signal is free from excess timing variations and its transitions are fast enough to preserve the critical data values the signal is meant to deliver. These tests, which require uncompromised performance on the part of the measurement toolset, detect aberrations and signal degradation that arise from distributed capacitance, resistance, crosstalk, and more.

#### **Jitter Tests**

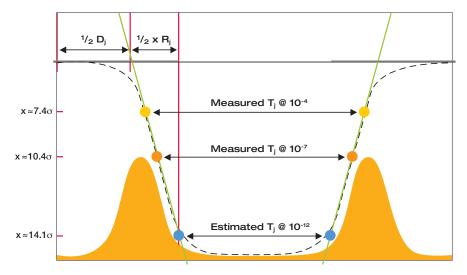

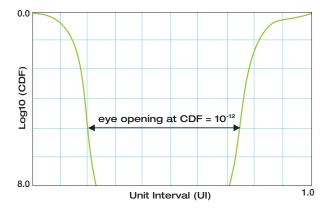

With faster data rates, jitter becomes one of the most difficult issues to resolve, which is one reason jitter measurements continue to be a topic of extensive discussion in standards bodies' working groups. It is also a focus of companies that develop specialized analysis tools to help you quickly identify the causes and results of jitter and to understand this complex issue.

Jitter is a result of spectral components, both deterministic and random. To guarantee interoperability, the transmitter must not develop too much jitter, and the receiver must be able to tolerate a defined amount of jitter and still recover the clock and de-serialize the data stream. Other signal characteristics, such as amplitude and rise time can affect any jitter tolerance property. In effect, jitter is a bit error ratio measurement and is usually quantified in terms of total jitter at a specified bit error ratio (BER).

| Test                               | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|